# (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 105470217 B (45)授权公告日 2019. 08. 27

(21)申请号 201510626500.0

(22)申请日 2015.09.28

(65)同一申请的已公布的文献号 申请公布号 CN 105470217 A

(43)申请公布日 2016.04.06

(30)优先权数据

14/499,216 2014.09.28 US

(73) **专利权人** 德克萨斯仪器股份有限公司 地址 美国德克萨斯州

(72)发明人 A·维诺戈帕 M·丹尼森

L•哥伦布 S•彭德哈卡

(74)专利代理机构 北京纪凯知识产权代理有限 公司 11245

代理人 赵蓉民 赵志刚

(51) Int.CI.

H01L 23/367(2006.01)

*H01L 23/373*(2006.01)

*H01L* 21/50(2006.01)

(56)对比文件

US 2007/0148963 A1,2007.06.28,

US 6407922 B1,2002.06.18,

CN 103547441 A,2014.01.29,

US 2003/0209802 A1,2003.11.13,

审查员 肖瑶

权利要求书2页 说明书6页 附图6页

### (54)发明名称

用于BEOL热管理的散热器的集成

#### (57)摘要

本发明涉及用于BEOL热管理的散热器的集成。一种微电子装置(100),包括组件(104)的电极(114)和电极(116)上的散热器层(118)和散热器层(120)以及散热器层(118)和散热器层(120)上的金属互连件(122)和金属互连件(124)。散热器层(118)和散热器层(120)被布置在半导体装置(100)的基板(102)的顶表面上方。散热器层(118)和散热器层(120)的厚度为100纳米至3微米,具有至少150瓦/(米•开尔文)的面向热导率以及小于100微欧姆•厘米的电阻率。

1.一种集成电路,包括:

具有表面的半导体基板:

形成在所述半导体基板内并且具有在所述表面上方的电极的电子组件,所述电极连接 到所述电子组件的端子;

散热器层,其定位在所述电极上方并且包括石墨、碳纳米管层和/或多个石墨烯层,所述散热器层相对于所述表面横向连续延伸超过所述端子的横向范围并且具有至少150瓦特/米•开尔文的面向热导率:以及

定位在所述散热器层上方的金属层。

- 2.根据权利要求1所述的集成电路,其中所述散热器层具有范围从100纳米至3微米的厚度,并且所述厚度被定义成垂直于所述面向热导率的面向方向。

- 3.根据权利要求1所述的集成电路,其中所述散热器层包括小于100微欧姆·厘米的电阻率。

- 4.根据权利要求1所述的集成电路,其中所述散热器层包括连续有孔模式。

- 5.根据权利要求1所述的集成电路,进一步包括:

半导体基板,其定义与所述电子组件邻近的基板孔,

其中所述散热器层延伸超过所述电极并且进入所述基板孔中。

6.一种集成电路,包括:

具有表面的基板:

电子组件,其具有连接到所述电子组件的第一端子的第一电极和连接到所述电子组件的第二端子的第二电极,所述第一电极和第二电极中的每个定位在所述表面上方;

散热器层,其包含石墨、碳纳米管层和/或多个石墨烯层,所述散热器层具有至少150瓦特/米•开尔文的面向热导率,所述散热器层具有第一区段和与所述第一区段隔离的第二区段,所述第一区段定位在所述第一电极上方并且相对于所述表面横向连续延伸超过所述第一端子的横向范围,所述第二区段定位在所述第二电极上方并且相对于所述表面横向连续延伸超过所述第二端子的横向范围;以及

金属层,其具有第一部分和第二部分,所述散热器层的所述第一区段位于所述第一部分和所述第一电极之间,并且所述散热器层的所述第二区段位于所述第二部分和所述第二电极之间。

- 7.根据权利要求6所述的集成电路,其中所述散热器层具有范围从100纳米至3微米的厚度,并且所述厚度被定义成垂直于所述面向热导率的面向方向。

- 8.根据权利要求6所述的集成电路,其中所述散热器层包括至少100微欧姆·厘米的电阻率。

- 9.根据权利要求6所述的集成电路,其中:

所述散热器层的所述第一区段与所述第一电极是相连的;并且 所述散热器层的所述第二区段与所述第二电极是相连的。

10.根据权利要求6所述的集成电路,其中:

所述散热器层的所述第一区段与所述金属层的所述第一部分是相连的;并且所述散热器层的所述第二区段与所述金属层的所述第二部分是相连的。

11.根据权利要求6所述的集成电路,其中所述散热器层包括连续有孔模式。

12.根据权利要求6所述的集成电路,进一步包括:

半导体基板,其定义与所述电子组件邻近的基板孔,

其中所述散热器层延伸超过所述第一电极和所述第二电极并且进入所述基板孔中。

# 用于BE0L热管理的散热器的集成

### 技术领域

[0001] 本发明涉及微电子装置领域。更具体地,本发明涉及微电子装置中的热管理结构。

### 背景技术

[0002] 具有局部发热组件的半导体装置经历热点,这会导致降低的可靠性。去除热量同时保持期望的成本和结构形式因素已经成为问题。

## 发明内容

[0003] 下面提供简单的概述以提供对本发明的一个或更多方面的基本理解。此概述不是本发明的广泛综述,并且并不旨在确定本发明的关键或重要元素,也不旨在描绘其范围。相反,该概述的主要目的是以简化的形式呈现本发明的一些概念,作为之后呈现的具体实施方式的前序。

[0004] 一种微电子装置包括组件的电极上的散热器层和散热器层上的金属互连件。散热器层被布置在半导体装置的基板的顶表面上方。散热器层的厚度为100纳米至3微米、具有至少150瓦特/(米•开尔文)的面向热导率以及小于100微欧姆•厘米的电阻率。

## 附图说明

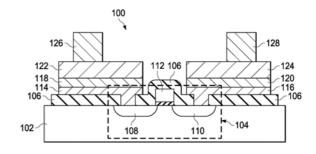

- [0005] 图1是包括散热器层的一个示例性微电子装置的截面。

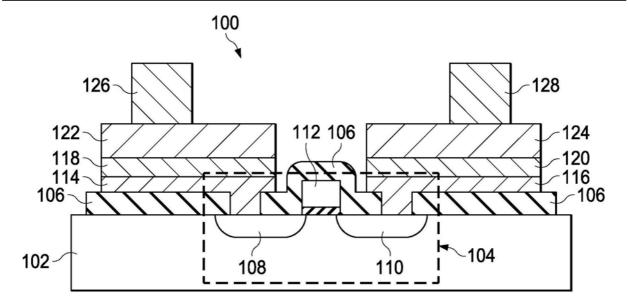

- [0006] 图2是包括散热器层的另一个示例性微电子装置的截面。

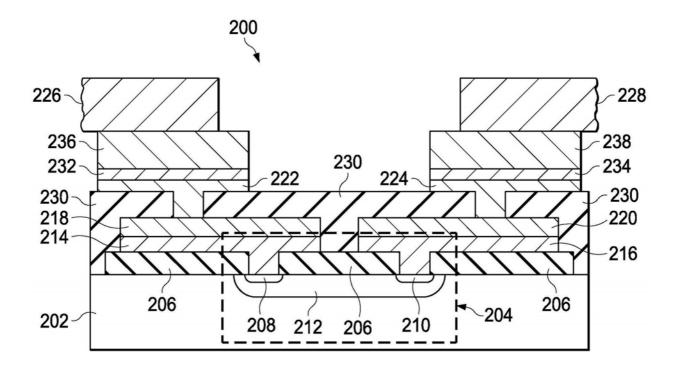

- [0007] 图3是包括散热器层的一个进一步示例性微电子装置的截面。

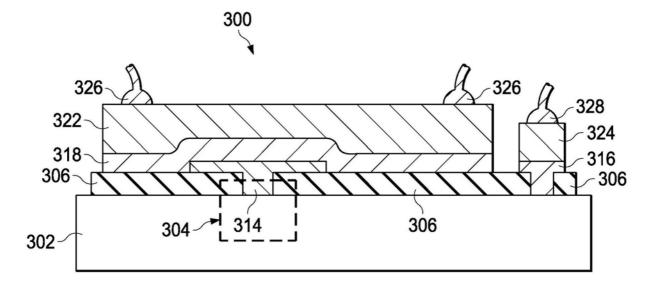

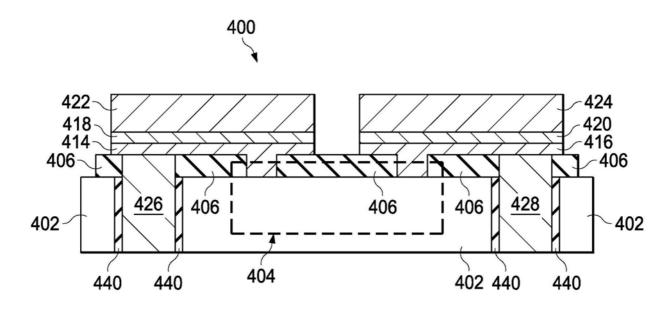

- [0008] 图4是包括散热器层的另一个示例性微电子装置的截面。

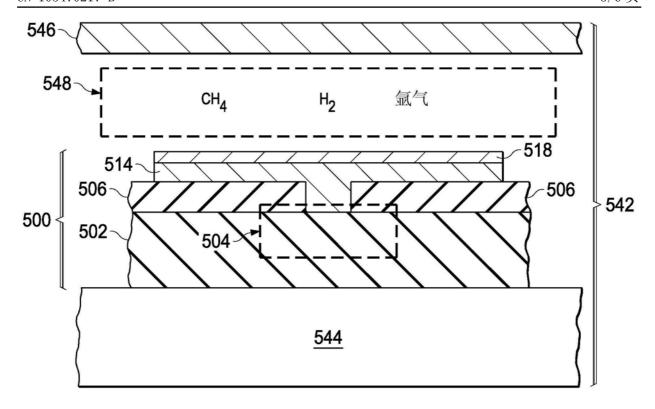

- [0009] 图5描绘用于在微电子装置上形成散热器层的一个示例性方法。

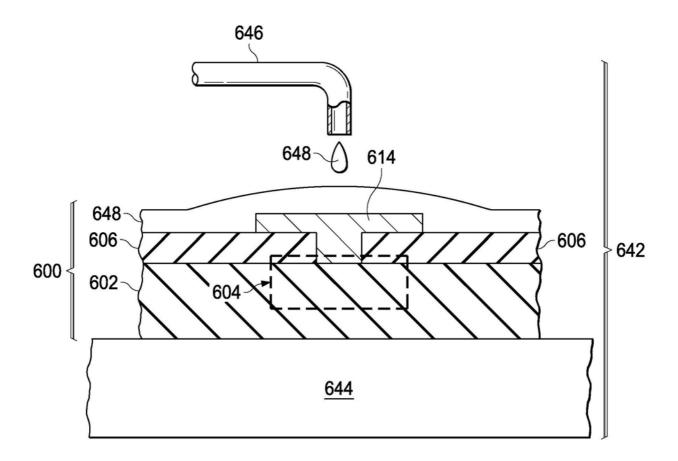

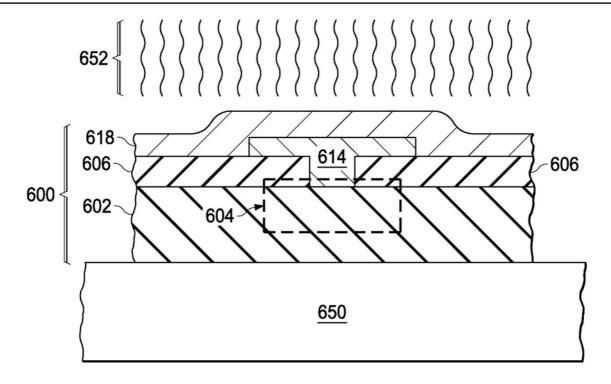

- [0010] 图6A和图6B描绘用于在微电子装置上形成散热器层的另一个示例性方法。

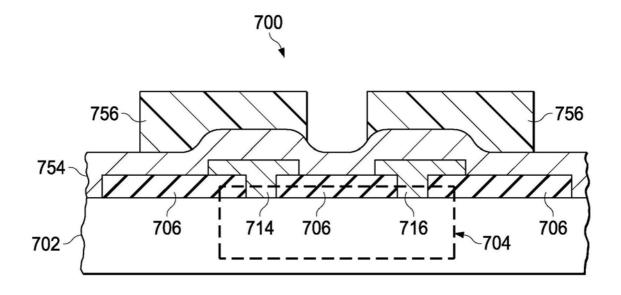

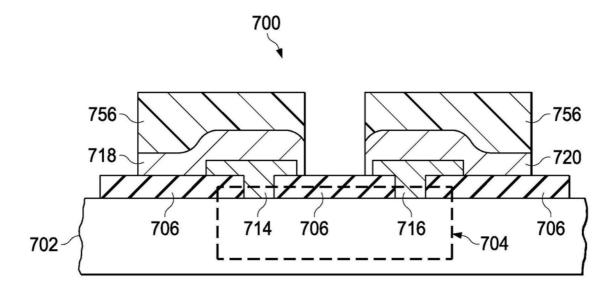

- [0011] 图7A和图7B描绘用于在微电子装置中图案化散热器层的一个示例性方法。

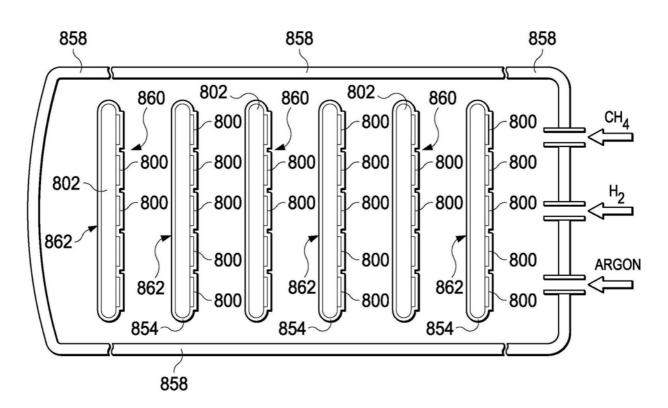

- [0012] 图8描绘用于在微电子装置上形成散热器层的一个进一步示例性方法。

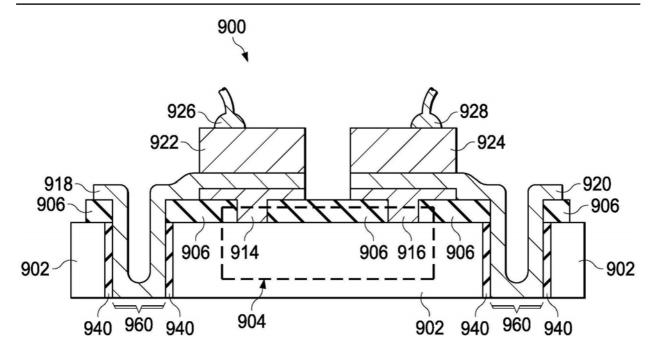

- [0013] 图9是包括散热器层的一个进一步示例性微电子装置的截面。

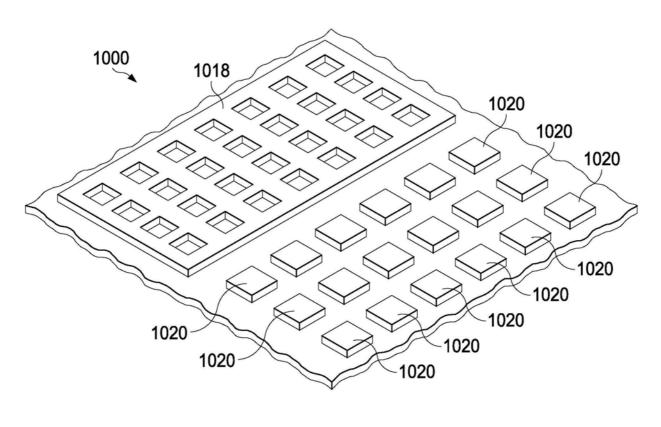

- [0014] 图10描绘图案化的散热器层的示例性构型。

#### 具体实施方式

[0015] 下列未决专利申请是相关的并且通过引用纳入本文:美国专利申请12/xxx,xxx (德州仪器案卷号TI-73379与此申请同时提交)。

[0016] 参照附图描述本发明。这些附图不是按比例绘制的并且提供它们仅为了说明本发明。以下参照用于说明的多个示例性应用描述本发明的一些方面。应当理解,阐述许多具体细节、关系和方法以提供对本发明的理解。然而,相关领域的技术人员将容易理解,能够在没有这些具体细节中的一个或更多或者使用其他方法来实现本发明。在其他实例中,没有详细示出已知结构或操作以避免混淆本发明。本发明不受所示的动作或者事件的顺序所限

制,因为某些动作可以以不同的顺序发生和/或与其他动作或者事件同时发生。此外,并不要求所有示出的动作或者事件实现根据本发明的方法。

图1是包括散热器层的一个示例性微电子装置的截面。在基板102(诸如半导体基 板102)上形成微电子装置100。微电子装置100包含组件104,该组件104在当前示例中被描 绘成金属氧化物半导体 (MOS) 晶体管104,其形成在基板102中和基板102上。在其他示例中, 组件104可以是电阻器、二极管、双极型晶体管、另外类型的晶体管或者在微电子装置100的 操作期间生成热量的其他组件。微电子装置100可以包括在基板102上方的电介质层106以 将节点(诸如MOS晶体管104的源极108、漏极110和栅极112)电气隔离。微电子装置100包括 接触源极108的源极电极114和接触漏极110的漏极电极116。源极电极114和漏极电极116可 以包括例如钛或钛钨的衬垫和在该衬垫上、具有少量百分比的钛、铜和/或硅的铝层,并且 源极电极114和漏极电极116可以被同时形成。微电子装置100包括形成在源极电极114上的 第一散热器层118以及形成在漏极电极116上的第二散热器层120。第一散热器层118和第二 散热器层120可以同时形成,并且被分离以在源极电极114和漏极电极116之间提供电隔离。 在第一散热器层118上形成第一金属互连件122以及在第二散热器层120上形成第二金属互 连件124。第一金属互连件122和第二金属互连件124可以同时形成,并且可以包括,例如钛 或钛钨的粘合层、在该粘合层上方、具有少量百分比的钛、铜和/或硅的铝层和铝层上方的 钛、钛钨或氮化钛的覆盖层。微电子装置100包括电耦合到第一金属互连件122的第一键合 结构126并且包括电耦合到第二金属互连件124的第二键合结构128。在当前示例中,第一键 合结构126和第二键合结构128是凸块键合柱126和凸块键合柱128。在其他示例中,第一键 合结构126和第二键合结构128可以是线键合、梁式引线、贯穿基板通孔或条带键合(clip)。 第一散热器层118和第二散热器层120具有相同的构成和结构。第一散热器层118 和第二散热器层120的厚度为100纳米至3微米。散热器层118和散热器层120具有至少150瓦 特/(米•开尔文)的面向热导率以及小于100微欧姆•厘米的电阻率。术语面向热导率是指 散热器层中的横向热导率,即,平行于基板的顶表面。散热器层118和散热器层120可以包 括,例如石墨、纳米碳管(CNT)层和/或多层石墨烯。在当前示例中,第一散热器层118和第二 散热器层120分别与源极电极114和漏极电极116基本相连(coterminous),并且第一金属互 连件122和第二金属互连件124分别与第一散热器层118和第二散热器层120基本相连。在微 电子装置100操作期间,可以在组件104中生成热量。散热器层118和散热器层120横向地将 热量传导远离组件104,到达第一键合结构126和第二键合结构128,相比于没有散热器层的 微电子装置,有利地降低组件104中的温度上升。在当前示例的一个替代版本中,微电子装 置100可以包括在源极电极114和漏极电极116以及第一散热器层118和第二散热器层120之 间的金属互连件的一个或更多附加级。在一个进一步版本中,微电子装置100可以包括在第 一散热器层118和第二散热器层120以及第一键合结构126和第二键合结构128之间的金属 互连件的一个或更多附加级。

[0019] 图2是包括散热器层的另一个示例性微电子装置的截面。在基板202 (诸如半导体基板202)上形成微电子装置200。微电子装置200包含组件204,该组件204被描述为在基板202中具有扩散层212的电阻器204。微电子装置200包括在基板202上方、在电阻器204的第一头部208和第二头部210处具有开口的第一电介质层206。微电子装置200包括接触第一头部208的第一电极214和接触第二头部210的第二电极216。第一电极214和第二电极216可以

包括与图1的源极电极114和漏极电极116相似的层和构成。微电子装置200包括形成在第一电极214上的第一散热器层218和形成在第二电极216上的第二散热器层220。第一散热器层218和第二散热器层220可以同时形成,并且被分开以在第一电极214和第二电极216之间提供电气隔离。微电子装置200包括在第一散热器层218和第二散热器层220上具有开口的第二电介质层230。在第二电介质层230上方形成第一金属互连件222,与第一散热器层218进行接触;在第二电介质层230上方形成第二金属互连件224,与第二散热器层220进行接触。第一金属互连件222和第二金属互连件224可以同时形成并且可以具有与图1的第一金属互连件122和第二金属互连件124相似的层和构成。在第一金属互连件222上形成第三散热器层232以及在第二金属互连件224上形成第四散热器层234。在第三散热器层232上形成第三金属互连件236以及在第四散热器层234上形成第四金属互连件238。第三金属互连件236和第四金属互连件238可以具有与第一金属互连件222和第二金属互连件224相似的层和构成。替代地,第三金属互连件236和第四金属互连件236和第四金属互连件236的第一键合结构226并且包括电耦合到第四金属互连件238的第二键合结构228。在当前示例中,第一键合结构226和第二键合结构228是梁式引线(beam lead) 226和梁式引线228。

[0020] 第一散热器层218、第二散热器层220、第三散热器层232以及第四散热器层234具有如参照图1的第一散热器层118和第二散热器层120所描述的相同的性质。在微电子装置200操作期间,可以在组件204中生成热量。散热器层218、220、232和234横向地将热量传导远离组件204到达第一键合结构226和第二键合结构228,相比于没有散热器层的微电子装置,有利地降低组件204中的温度上升。在金属互连件的第一级(即,第一金属互连件222和第二金属互连件224)上和金属互连件的第二级(即,第三金属互连件236和第四金属互连件238)上形成散热器层218、220、232和234,相比于散热器层在仅一级金属互连件上的微电子装置而言,可以有利地进一步降低组件204中的温度上升。

[0021] 图3是包括散热器层的一个进一步示例性微电子装置的截面。在基板302上形成微电子装置300。微电子装置300包含形成在基板302中和/或基板302上的组件304。微电子装置300可以包括在基板302上方的电介质层306,电介质层306具有在组件304上的开口以及用于另一个组件或另外的连接的可能的另一个开口。在组件304上形成第一电极314,其可能在电介质层306上方部分延伸。可以形成第二电极316,其可能与第一电极314同时形成,以建立与另一个组件的连接或者到组件304的另外的连接(如到组件304的栅极的连接)。在第一电极314上形成散热器层318。在当前示例中,散热器层318延伸超过第一电极314到电介质层306上,但不接触第二电极316。在当前示例中,第二电极316远离散热器层。在散热器层318上形成第一金属互连件322以及在第二电极316上形成第二金属互连件324。第一金属互连件322和第二金属互连件324可以同时形成。在第一金属互连件322上形成多个第一接合结构326以提供电耦合到第一金属互连件322的键合结构;在第二金属互连件324上形成第二键合结构328。在当前示例中,键合结构326和键合结构328是线键合。在当前示例中,散热器层在第一键合结构326下方延伸。

[0022] 散热器层318具有如参照图1的第一散热器层118和第二散热器层120所描述的相同的性质。在微电子装置300操作期间,可以在组件304中生成热量。形成延伸超过第一电极314并在第一键合结构326下方延伸的散热器层318横向地将热量传导远离组件304到达多

个第一键合结构326,相比于没有散热器层的微电子装置而言,有利地降低组件304中的温度上升。

[0023] 图4是包括散热器层的另一个示例性微电子装置的截面。在基板402上形成微电子装置400。微电子装置400包含形成在基板402中和/或基板402上的组件404。微电子装置400可以包括在基板402上方的电介质层406,电介质层406具有在组件404上的开口和用于键合结构426和键合结构428的开口,在当前示例中,所述开口是贯穿基板通孔426和贯穿基板的通孔428并由电介质衬垫440与基板402电气隔离。第一电极414形成在组件404上并且在电介质层406上方延伸以接触第一贯穿基板通孔426的顶部。第二电极416形成在组件404上形成并且在电介质层406上方延伸以接触第二贯穿基板通孔428的顶部。在第一电极414上形成的第一散热器层418在组件404上方和第一贯穿基板通孔426上方部分延伸。在第二电极416上形成的第二散热器层420在组件404上方和第二贯穿基板的通孔428上方部分延伸。在第一散热器层418上形成的第一金属互连件422在组件404上方和第一贯穿基板通孔426上方部分延伸。在第二散热器层420上形成的第二金属互连件424在组件404上方和第二贯穿基板通孔428上方部分延伸。第一金属互连件422有利地在组件404和第一贯穿基板通孔426之间提供低阻抗电气通路,并且第二金属互连件424有利地在组件404和第二贯穿基板通孔428之间提供低阻抗电气通路。

[0024] 第一散热器层418和第二散热器层420具有如参照图1的第一散热器层118和第二散热器层120所描述的相同的性质。在微电子装置400操作期间,可以在组件404中生成热量。形成从组件404延伸至贯穿基板通孔426和贯穿基板通孔428的散热器层418和散热器层420横向地将热量传导远离组件404到达贯穿基板通孔426和贯穿基板通孔428,相比于没有散热器层的微电子装置,有利地降低组件404中的温度上升。

[0025] 图5描绘用于在微电子装置上形成散热器层的一个示例性方法。在基板502(其可以是例如半导体晶片)上形成微电子装置500。在基板502中和/或基板502上形成组件504。在基板502上方形成电介质层506,其具有在组件504上的开口。在电介质层506的开口中的组件504上形成电极514,电极514在电介质层506上方、围绕该开口部分延伸。电极514被图案化使得该电极在期望区域上方延伸但不在整个基板502上方延伸。将认识到,微电子装置500的多个实例可以在基板502上同时形成。

[0026] 微电子装置500被放置在加热的基板座544上的等离子体增强化学气相沉积 (PECVD) 室542中。PECVD室542具有位于基板座544上方的等离子体电极板546,从而使得微电子装置500被放置在等离子体电极板546下方。微电子装置500由基板座544加热至400℃至500℃,并且碳反应物气体如甲烷(CH4)与减少的反应物气体(如氢气)以及等离子体辅助气体(如氩气)被引入到等离子体区域548。将13.56MHz的射频(RF)功率应用到等离子体电极板546,使得等离子体区域中的反应物气体在等离子体区域548中形成等离子体,产生碳自由基,其在微电子装置500的电极514上形成石墨层518。可以选择RF功率、基板座544温度以及反应物气体的压力和流量速率,使得石墨518在电极514上但不在相邻的电介质层506上选择性地生长。石墨层518提供微电子装置500的散热器层518。在电极514上但不在相邻的电介质层506上选择性地形成石墨层518可以消除对石墨层518的图案化并且因此有利地降低微电子装置500的制造成本和复杂性。

[0027] 在被称为微波辅助表面波等离子体化学气相沉积 (MW-SWP-CVD) 工艺的当前示例

的另一个版本中,微电子装置500可以被加热至220℃到260℃,并且微波频率下的RF功率可以被施加到等离子体电极板546,在等离子体区域548中形成微波等离子体,并且随后形成石墨层518。使用MW-SWP-CVD工艺形成石墨层518可以有利地减小微电子装置500的组件504和其他组件上的热应力。

[0028] 图6A和图6B描绘用于在微电子装置上形成散热器层的另一个示例性方法。参照图 6A,在基板602(其可以是例如半导体晶片)上形成微电子装置600。在基板602中和/或基板602上形成组件604。在基板602上方形成电介质层606,其在组件604上具有开口。在电介质层606的开口中的组件604上形成电极614,电极614在电介质层606上方、围绕该开口部分延伸。电极614被图案化以使电极在期望区域上方延伸但不在整个基板602上方延伸。将认识到,微电子装置600的多个实例可以在基板602上同时形成。

[0029] 微电子装置600被放置在基板卡盘644上的旋转涂覆设备642中。分散设备646在电极614和电介质层606的暴露区域上提供CNT分散剂648。CNT分散剂648包括分散在溶剂中的多个CNT。基板卡盘旋转以扩散CNT分散剂648,以便涂覆微电子装置600。

[0030] 参照图6B,微电子装置600被放置在烘焙卡盘650上,该烘焙卡盘将基板602加热至100℃至150℃,以便蒸发来自图6A的CNT分散剂648的溶剂652以提供散热器层618。散热器层618因此包括在连续层中互相重叠的CNT。形成包括CNT的散热器层618有利地提供高面向热导率。使用图6A和图6B的旋转涂覆工艺形成散热器层618有利地减小微电子装置500的热剖面并且相比于真空沉积设备有利地利用更低成本的设备。

[0031] 图7A和图7B描绘用于在微电子装置中图案化散热器层的一个示例性方法。参照图7A,在基板702上形成微电子装置700。在基板702中和/或基板702上形成组件704。在基板702上方形成电介质层706,其在组件704上具有开口。在电介质层706的开口中的组件704上形成第一电极714和第二电极716,第一电极714和第二电极716在电介质层706上方、围绕该开口部分延伸。在在第一电极714、第二电极716和电介质层706上方形成连续的散热器材料层754。散热器材料层754可以包括例如石墨、CNT和/或多层石墨烯。在第一电极714和围绕第一电极714的电介质层706的一部分上方以及第二电极716和围绕第二电极716的电介质层706的一部分上方的散热器材料层754的上方形成蚀刻掩模756。蚀刻掩模756可以包括例如由光刻工艺形成的光刻胶。

[0032] 参照图7B,蚀刻工艺移除由蚀刻掩模756暴露的区域中的图7A的散热器材料层754,留下第一电极714上的第一散热器层718以及第二电极716上的第二散热器层720。随后,例如通过溶剂喷射工艺,移除蚀刻掩模756,以便不移除第一散热器层718和第二散热器层720的重要部分。通过在第一散热器层718上形成第一金属互连件以及在第二散热器层720上形成第二金属互连件,继续制造微电子装置700。使用蚀刻掩模756将图7A的散热器材料层754图案化可以有利地形成具有期望面积的散热器层718和散热器层720,包括到相邻电介质层706的重叠。

[0033] 图8描绘用于在微电子装置上形成散热器层的一个进一步示例性方法。在一个或更多基板802上形成多个微电子装置800。基板802可以是例如半导体晶片。每个半导体装置800包括组件和形成在组件上的电极,这些半导体装置形成在相应基板802的前表面860处。每个基板802具有与前表面860相对的后表面862。基板802放置在如炉管的沉积室858中,使得每个基板802的前表面860和后表面862暴露于沉积室858的环境中。反应物气体如甲烷、

氢气和氩气被引入到沉积室858中并且基板802被加热。可以施加RF功率以在反应物气体中形成等离子体。反应物气体在每个基板802的前表面860和后表面862上同时地形成散热器材料层854。随后从沉积室858中将基板802移除。例如,如参照图7A和图7B所描述的,可以在每个基板802的前表面860上图案化散热器材料层854,以在微电子装置800上形成散热器层。可以在每个基板802的后表面862上将该散热器材料层854图案化以形成可以有利地降低组件的温度上升的背侧散热器层,如共同受让的具有专利申请序列号xx/xxx,xxx(律师卷号为TI-73379)的专利申请(其与本申请同时提交)所描述的,其通过引用结合到本文。在前表面860和后表面862上同时形成散热器材料层854可以有利地减少微电子装置800的制造成本和复杂性。

[0034] 图9是包括散热器层的一个进一步示例性微电子装置的截面。在基板902上形成微电子装置900。基板902具有由电介质衬垫940包围的基板孔960;如在图9中描绘的,这些基板孔960可以完全贯穿基板902延伸至基板902的后表面。微电子装置900包含形成在基板902中和/或基板902上的组件904。微电子装置900包括在基板902上方的电介质层906,电介质层906在组件904上以及在这些基板孔处960具有开口。第一电极914形成在组件904上并且在电介质层906上方延伸,以及第二电极916形成在组件904上并且在电介质层906上方延伸。形成在第一电极914上的第一散热器层918延伸到至少一个基板孔960中。形成在第二电极916上的第二散热器层920延伸到至少另一个基板孔960中。在第一散热器层918上形成第一金属互连件922以及在第二散热器层920上形成第二金属互连件924。在第一金属互连件922上形成第一键合结构926以及在第二金属互连件924上形成第二键合结构928。在当前示例中,键合结构926和键合结构928是线键合。形成延伸到基板孔960中的散热器层918和散热器层920可以将热量从组件904传导至基板902的后表面并且有利地降低组件904中的温度上升。图9的构型针对安装在引线框或者头座(其在基板902的后表面上具有芯片附接材料)上的微电子装置900的实例可以是特别有利的。

[0035] 图10描绘图案化的散热器层的示例性构型。微电子装置1000可以包括连续且有孔的、具有孔阵列的第一散热器层1018。该有孔构型相比于无孔的散热器层可以有利地增加第一散热器层1018与微电子装置1000的下面层的粘合。第一散热器层1018的连续有孔构型相比于分段散热器层可以有利地具有更高的横向热传导性。

[0036] 微电子装置1000可以具有第二散热器层1020,其是分段的并包括多个分隔区域。该分段构型可以有利地增加第二散热器层1020与下面层的粘合。可以在分开的电极上形成第二散热器层1020的区段而不短路电极。分段构型相比于在电气隔离的电极上方没有散热器层的微电子装置,可以有利地在多个下面电气隔离的电极上方具有增加的横向热量传导性。微电子装置可以具有散热器层,该散热器层在一个区域中具有连续有孔构型而在另一个区域中具有分段构型。

[0037] 虽然以上已经描述了本发明的不同实施例,但应理解,这些实施例仅通过举例而不是限制性的方式来呈现。能够根据在此的披露,在不背离本发明的精神和范围的情况下对所披露的实施例作出各种改变。因此,本发明的幅度和范围不应当受任何一个以上描述的实施例的限制。而是,本发明的范围应当根据以下权利要求书及其等同体来限定。

图1

图2

图3

图4

图5

图6A

图6B

图7A

图7B

图8

图9

图10