# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110637360 B (45) 授权公告日 2020. 12. 22

(21)申请号 201880031656.6

(22) 申请日 2018.06.12

(65) 同一申请的已公布的文献号 申请公布号 CN 110637360 A

(43) 申请公布日 2019.12.31

(30) 优先权数据 15/696,962 2017.09.06 US

(85) PCT国际申请进入国家阶段日 2019.11.13

(86) PCT国际申请的申请数据 PCT/US2018/037031 2018.06.12

(87) PCT国际申请的公布数据 W02019/050585 EN 2019.03.14

(73) 专利权人 谷歌有限责任公司 地址 美国加利福尼亚州 (72) 发明人 梅勒妮·博谢敏 马德胡苏丹·延加尔 克里斯托弗·马隆 格雷戈里·里姆瓦尔

(74) 专利代理机构 中原信达知识产权代理有限 责任公司 11219

代理人 李佳 邓聪惠

(51) Int.CI.

H01L 23/38 (2006.01)

(56) 对比文件

CN 103137577 A,2013.06.05

US 2015035134 A1,2015.02.05

CN 103378017 A,2013.10.30

CN 104716109 A, 2015.06.17

审查员 赵端

权利要求书2页 说明书7页 附图8页

### (54) 发明名称

用于2.5D/3D IC封装的定点冷却的热电冷却器(TEC)

#### (57) 摘要

虽然使用2.5D/3D封装技术产生紧凑型IC封装,但是其同样针对热管理出现挑战。根据本公开的集成组件封装提供了一种用于包括与多个低功率组件集成的高功率组件的2.5D/3D IC封装的热管理解决方案。由本公开提供的所述热解决方案包括传统的散热器或者冷平板的被动式冷却和热电冷却(TEC)元件的主动式冷却的混合。根据本公开的某些方法包括:在包括位于邻近于高功率组件的多个低功率组件的IC封装中在正常操作期间控制温度,其中,所述高功率组件在正常操作期间相对于所述低功率组件中的每个低功率组件产生更多的热量。

### 1.一种集成组件封装,包括:

耦合至封装基板的表面的多个低功率组件和高功率组件,其中,所述低功率组件位于邻近于所述高功率组件,所述多个低功率组件和所述高功率组件中的每一个在正常操作期间产生热,并且所述高功率组件在正常操作期间相对于所述低功率组件中的每个低功率组件产生更多的热量;

封装盖,所述封装盖耦合至所述封装基板并且覆盖所述多个低功率组件和所述高功率组件:

冷平板,所述冷平板物理地热耦合至所述封装盖,所述冷平板包括基部表面和顶部表面,其中,所述顶部表面相对于所述封装盖与所述基部表面相对;以及

多个热电冷却TEC元件,其中,在所述集成组件封装内调整所述TEC元件的大小并且定位所述TEC元件,使得在与所述低功率组件和所述高功率组件所耦合的所述封装基板的所述表面垂直的方向中突出的相应TEC元件的占用区的至少实质部分与所述低功率组件中的至少一个低功率组件重叠,并且在与所述低功率组件和所述高功率组件所耦合的所述封装基板的所述表面垂直的所述方向中突出的所述TEC元件的所述占用区中没有部分与所述高功率组件重叠。

- 2.根据权利要求1所述的封装,其中,所述TEC被集成到所述冷平板中,使得每个TEC的第一侧被嵌入在所述冷平板的所述基部表面中并且每个TEC的第二侧物理地热耦合至所述封装盖。

- 3.根据权利要求2所述的封装,其中,所述冷平板的所述基部表面包括多个绝缘槽口,每个槽口定位在邻近于所述多个TEC中的一个TEC。

- 4.根据权利要求1所述的封装,其中,所述TEC被集成到所述封装盖中,使得每个TEC的第一侧被嵌入在所述封装盖中并且每个TEC的第二侧物理地热耦合至所述冷平板的所述基部表面。

- 5.根据权利要求1所述的封装,其中,所述TEC被集成到所述封装盖中,使得每个TEC的第一侧被嵌入在所述封装盖中并且每个TEC的第二侧物理地热耦合至所述低功率组件。

- 6.根据权利要求1所述的封装,其中,所述TEC被集成到所述封装盖中,使得每个TEC的第一侧被耦合并且热耦合至所述冷平板的所述基部表面并且每个TEC的第二侧物理地热耦合至所述低功率组件。

- 7.根据权利要求1所述的封装,其中,每个TEC的第一侧被嵌入在所述封装基板中,并且每个TEC的第二侧物理地热耦合至所述低功率组件。

- 8.根据权利要求1所述的封装,其中,每个TEC是独立供电的。

- 9.一种组装集成组件封装的方法,所述方法包括:

将多个低功率组件和高功率组件耦合至封装基板的表面,其中,所述低功率组件位于邻近于所述高功率组件,所述多个低功率组件和所述高功率组件中的每一个在正常操作期间产生热,并且所述高功率组件在正常操作期间相对于所述低功率组件中的每个低功率组件产生更多的热量;

将封装盖耦合至所述封装基板,其中,所述封装盖覆盖所述多个低功率组件和所述高功率组件;

将冷平板物理地热耦合至所述封装盖,所述冷平板包括基部表面和顶部表面,其中,所

述顶部表面相对于所述封装盖与所述基部表面相对:以及

在所述集成组件封装内调整多个热电冷却TEC元件的大小并且定位多个热电冷却TEC元件,使得在与所述低功率组件和所述高功率组件所耦合的所述封装基板的所述表面垂直的方向中突出的相应TEC元件的占用区的至少实质部分与所述低功率组件中的至少一个低功率组件重叠,并且在与所述低功率组件和所述高功率组件所耦合的所述封装基板的所述表面垂直的所述方向中突出的所述TEC元件的所述占用区中没有占用区与所述高功率组件重叠。

- 10.根据权利要求9所述的方法,进一步包括:将所述TEC集成到所述冷平板中,使得每个TEC的第一侧被嵌入在所述冷平板的所述基部表面中并且每个TEC的第二侧物理地热耦合至所述封装盖。

- 11.根据权利要求10所述的方法,进一步包括:将多个绝缘槽口包括在所述冷平板的所述基部表面中,使得将每个槽口定位在邻近于所述多个TEC中的一个TEC。

- 12.根据权利要求10所述的方法,进一步包括:将所述TEC集成到所述封装盖中,使得每个TEC的第一侧被嵌入在所述封装盖中并且每个TEC的第二侧物理地热耦合至所述冷平板的所述基部表面,或者将所述TEC集成到所述封装盖中,使得每个TEC的第一侧被嵌入在所述封装盖中并且将每个TEC的第二侧物理地热耦合至所述低功率组件。

- 13.根据权利要求10所述的方法,进一步包括:将所述TEC集成到所述封装盖中,使得每个TEC的第一侧被耦合并且热耦合至所述冷平板的所述基部表面并且每个TEC的第二侧物理地热耦合至所述低功率组件,或者将所述TEC集成到所述封装盖中,使得每个TEC的第一侧被耦合并且热耦合至所述封装基板,并且将每个TEC的第二侧物理地热耦合至所述低功率组件。

- 14.根据权利要求10所述的方法,进一步包括:将所述TEC集成到所述封装盖中,使得每个TEC的第一侧被嵌入在所述封装基板中并且将每个TEC的第二侧物理地热耦合至所述低功率组件。

- 15.根据权利要求10所述的方法,进一步包括:为每个TEC独立地供电。

# 用于2.5D/3D IC封装的定点冷却的热电冷却器(TEC)

[0001] 相关申请

[0002] 本申请要求2017年9月6日提交的标题为"THERMOELECTRIC COOLER (TEC) FOR SPOT COOLING OF 2.5D/3D IC PACKAGES"的美国专利申请第15/696,962号的优先权和权益,其全部内容出于所有目的而通过引用的方式并入本文。

### 背景技术

[0003] 高带宽存储器 (HBM) 提供远远超越传统的存储器装置 (诸如,DDR4和GDDR5) 所能提供的存储器带宽,并且节省了成本和功率。HBM被设计为封装内存储器,并且通常位于处理器或者ASIC旁边。可以通过使用2.5D/3D封装技术来将多个HBM组件与单个ASIC集成。虽然使用2.5D/3D封装技术产生紧凑型IC封装,但是其同样针对热管理出现挑战。

### 发明内容

[0004] 根据一个方面,本公开中所描述的主题涉及一种集成组件封装,该集成组件封装包括:耦合至封装基板的表面的多个低功率组件和高功率组件。低功率组件位于邻近于高功率组件。多个低功率组件和高功率组件中的每一个在正常操作期间产生热,并且高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更高的热量。该封装包括:封装盖,该封装盖联接至封装基板并且覆盖多个低功率组件和高功率组件。该封装包括:冷平板,该冷平板物理地热耦合至封装盖,冷平板包括基部表面和顶部表面。冷平板的顶部表面相对于封装盖与冷平板的基部表面相对。该集成组件封装还包括:多个热电冷却(TEC)元件。TEC元件的大小和位置被设计为在该集成组件封装内,使得沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的相应TEC元件的占用区的至少大部分与低功率组件中的至少一个低功率组件重叠。TEC元件的大小和位置也被设计成使得沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的TEC元件的占用区基本上没有部分基本上与高功率组件重叠。

[0005] 根据另一方面,本公开中所描述的主题涉及一种组装集成组件封装的方法,该方法包括:将多个低功率组件和高功率组件耦合至封装基板的表面。低功率组件位于邻近于高功率组件。多个低功率组件和高功率组件中的每一个在正常操作期间产生热,并且高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更高的热量。该方法包括:将封装盖耦合至封装基板。该封装盖覆盖多个低功率组件和高功率组件。该方法包括:将为联查期,将平板包括基部表面和顶部表面。该顶部表面相对于封装盖与基部表面相对。该方法包括:在集成组件封装内调整多个热电冷却(TEC)元件的大小并且定位多个热电冷却(TEC)元件,使得沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的相应TEC元件的占用区的至少大部分与低功率组件中的至少一个低功率组件重叠,并且沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的TEC元件的占用区基本上没有部分基本上与高功率组件重叠。

[0006] 根据另一方面,本公开中所描述的主题涉及一种在集成组件封装中在正常操作期

间控制温度的方法,该集成组件封装包括覆盖邻近于高功率组件的多个低功率组件的封装盖,其中,高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更高的热量。该方法包括:在较高热敏性的局部区域处提供对封装盖进行特定位置冷却。较高热敏性的局部区域与由低功率组件产生的热相关联。在集成组件封装中在正常操作期间控制温度的方法还包括:在较低热敏性的局部区域处提供对封装盖进行冷却。较低热敏性的局部区域与由高温组件产生的热相关联。

### 附图说明

[0007] 如在附图中图示的,前述内容将通过下面的对本发明的示例实施方式的更具体的描述而显而易见。附图不一定按比例绘制,而是将重点放在说明本发明的实施方式上。

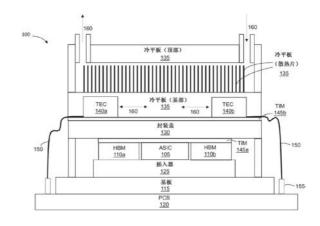

[0008] 图1A是根据示例实施方式的第一集成组件封装的侧视图的示意图。

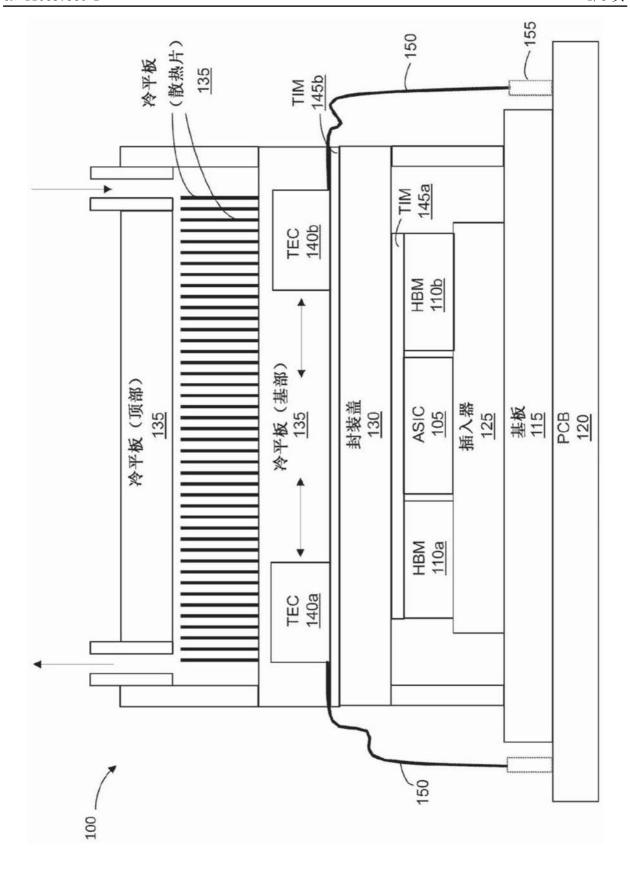

[0009] 图1B是在图1A中示出的集成组件封装的俯视图的示意图。

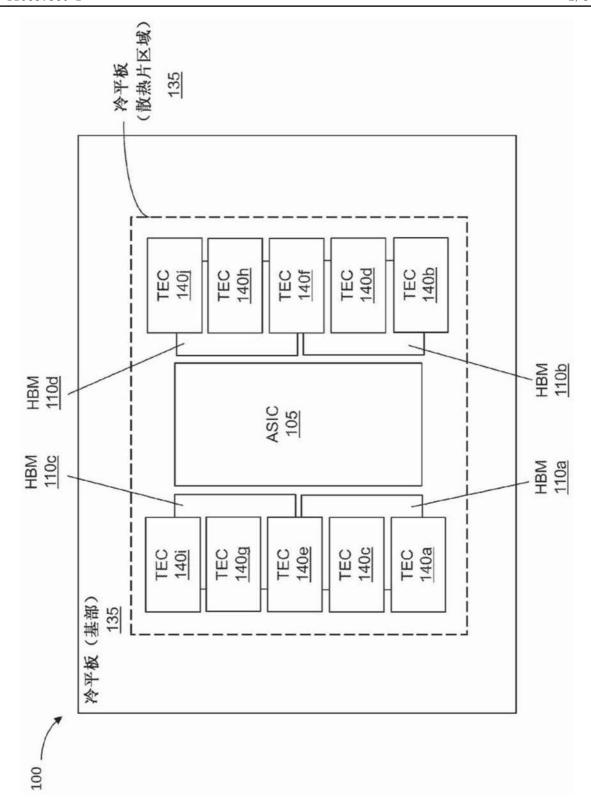

[0010] 图2是根据示例实施方式的第二集成组件封装的侧视图的示意图。

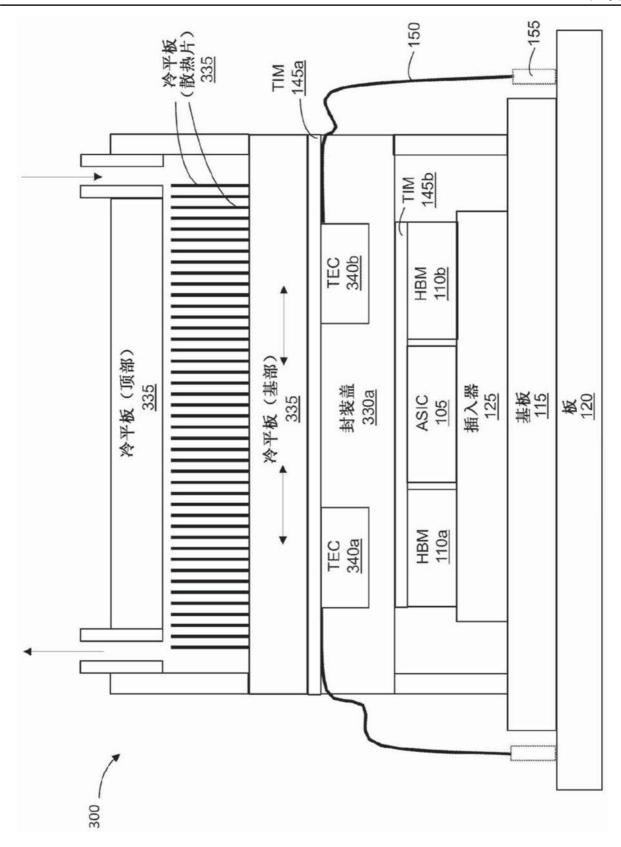

[0011] 图3是根据示例实施方式的第三集成组件封装的侧视图的示意图。

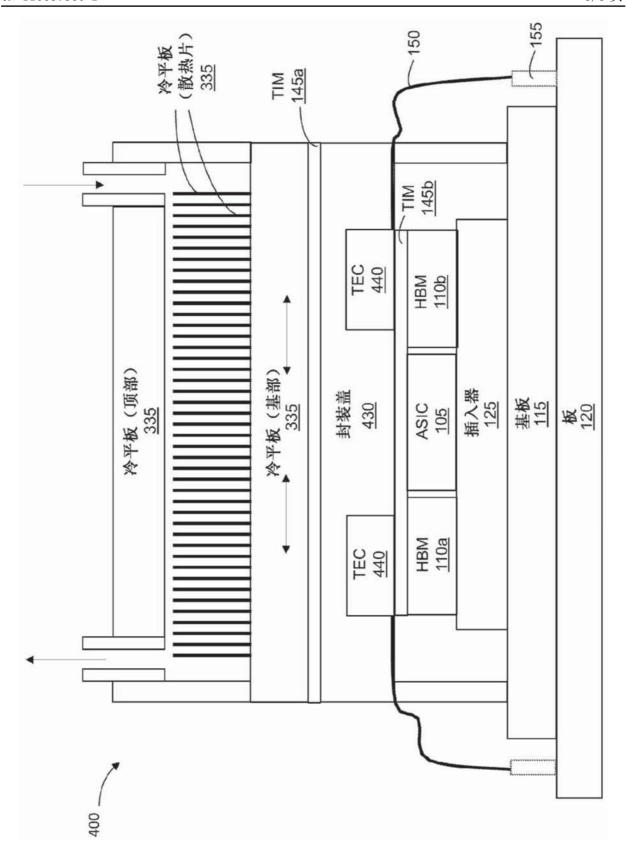

[0012] 图4是根据示例实施方式的第四集成组件封装的侧视图的示意图。

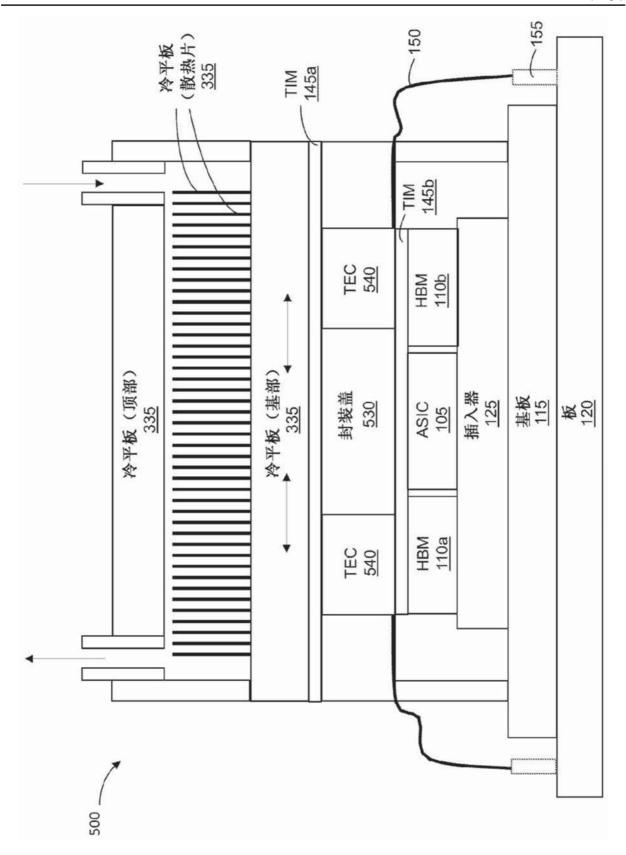

[0013] 图5是根据示例实施方式的第五集成组件封装的侧视图的示意图。

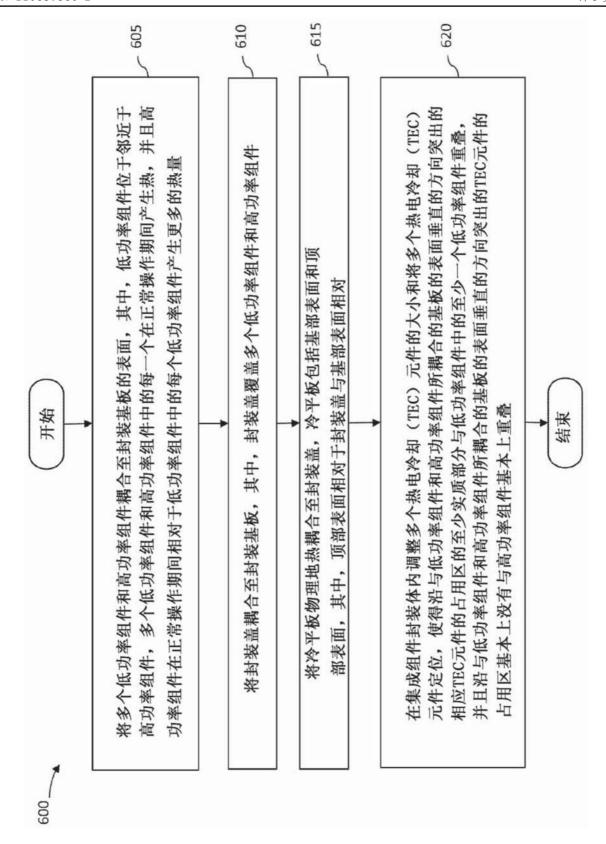

[0014] 图6是用于组装在图1至图5中示出的集成组件封装的方法的流程图。

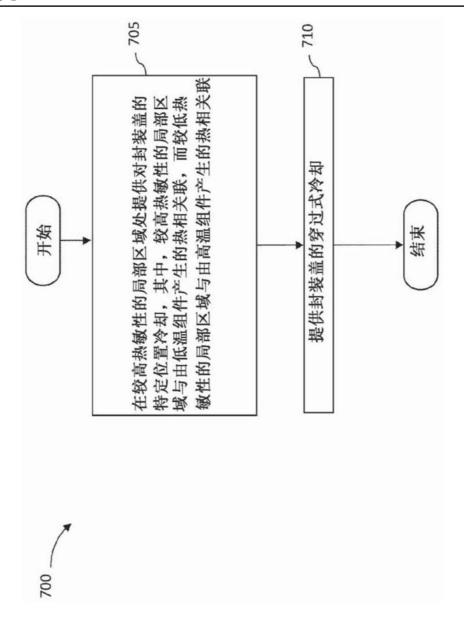

[0015] 图7是用于在图1至图5中示出的集成组件封装的正常操作期间控制温度的方法的流程图。

[0016] 为了清楚起见,并非会在每个附图中标记每个组件。不旨在按比例绘制附图。各个附图中的相同附图标记和标号指示相同的元件。

### 具体实施方式

高带宽存储器(HBM)提供远远超越传统的存储器装置(诸如,DDR4和GDDR5)所能提 供的存储器带宽,并且节省了成本和功率。HBM被设计为封装内存储器,并且通常位于处理 器或者ASIC旁边。可以通过使用2.5D/3D封装技术来将多个HBM组件与单个集成。虽然2.5D/ 3D封装技术产生紧凑型IC封装,但是其同样针对热管理出现挑战。示例2.5D/3D封装可以包 括被放置在由多个HBM组件围起的封装的中心处的ASIC。在这种封装配置中,在正常操作期 间,ASIC通常将使整个封装功率的大约90%分散。虽然HBM组件仅使整个封装功率的10%分 散,但是它们出于多种原因而驱动IC封装的热设计。首先,低功率HBM的内部热阻(结壳)通 常高于大功率ASIC的内部热阻(结壳)。此外,低功率HBM的最大结温(Tj)要求低于ASIC的最 大结温(Tj)要求。即,低功率HBM比高功率ASIC对温度更敏感。因此,对于低功率HBM组件,封 装的外壳温度或者Tcase(被定义为接触冷平板的基部的封装盖或者散热器的温度)要求将 远低于封装根本不包括低功率HBM组件或者低功率HBM组件比高功率ASIC具有更低的结壳 热阻的情况。因此,与这种封装一起使用的散热器(或者冷平板)通常需要具有非常低的热 阻(小于0.04C/W)以满足封装的目标Tcase要求。然而,对于散热器(或者冷平板)实现如此 低的热阻是复杂并且昂贵的。因此,需要具有一种用于2.5D/3D IC封装的热管理解决方案, 该2.5D/3D IC封装具有与多个低功率组件集成的高功率组件,该热管理解决方案在对封装 的散热器(或者冷平板)的热性能要求的影响减少的情况下降低了低功率组件在正常操作 期间的温度。

根据本公开的集成组件封装提供了一种用于2.5D/3D IC封装的热管理解决方案, 该2.5D/3D IC封装包括与多个低功率组件集成的高功率组件,该热管理解决方案降低了低 功率组件在正常操作期间的温度,而未对封装的散热器或者冷平板的热性能要求造成过度 影响。由本公开提供的热解决方案包括传统的散热器或者冷平板的被动式冷却和热电冷却 (TEC) 元件的主动式冷却的混合。通常,散热器或者冷平板冷却比TEC冷却更经济,因为对于 给定热源,随着在TEC元件的热侧与冷侧之间的温度梯度增加,TEC元件的性能系数(COP)可 以降低到远低于1。因此,根据本公开的实施方式利用散热器/冷平板来处理封装的大部分 散热,而在较高热敏性但是功耗较低(并且因此,生热性较低)的局部区域中,由TEC元件提 供辅助散热。例如,在包括低功率、对热更敏感的HBM组件和高功率、对热没那么敏感的ASIC 组件的封装中,TEC位于封装中,使得TEC元件的占用区通常与低功率HBM组件的部分重叠, 并且TEC元件的占用区基本上没有部分与高功率ASIC组件重叠。在一些实施方式中,TEC占 用区可以完全覆盖HBM组件。在一些实施方式中,TEC占用区可以仅覆盖HBM组件的表面积的 小部分。TEC元件相对于其它封装组件的放置帮助降低在覆盖低功率、对温度更敏感的HBM 组件的封装盖的局部区域处的温度。进一步地,将TEC元件放置在散热较低的局部区域中使 TEC元件暴露于在TEC元件的热侧与冷侧之间的较小的温度梯度,从而相对于接近高功率分 散组件的TEC,提高了TEC元件的COP。此外,将低功率HBM组件的冷却部分卸下到TEC元件允 许以较高的热阻(和较高的Tcase)使用更简单、更廉价的散热器(或者冷平板),同时仍然使 低功率HBM组件保持在其更严格的热规范内。

[0019] 根据本公开的某些方法包括:在包括邻近于高功率组件的多个低功率组件的IC封装中的正常操作期间控制温度,其中,高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更高的热量。用于控制在IC封装中的温度的方法进一步包括:在较高热敏性的局部区域处提供对封装盖进行特定位置冷却。较高热敏性的局部区域接近低功率组件,而较低热敏性的局部区域接近高功率组件。用于控制在IC封装中的温度的方法还包括:提供对封装盖进行传统的被动式冷却。在一些实施方式中,可以通过传统的被动式冷却来使包括由TEC元件冷却的区域的整个封装盖冷却。

[0020] 图1A是根据示例实施方式的第一集成组件封装100的侧视图的示意图。图1B是在图1A中示出的第一集成组件封装100的俯视图的示意图。第一集成组件封装100包括四个低功率组件,诸如,在图1B中示出的HBM 110a至110d(统称为HBM 110)。在图1A中仅示出了第一HBM 110a和第二HBM 110b。第一集成组件封装配置还包括高功率组件,诸如,ASIC 105。低功率HBM 110位于邻近于高功率ASIC 105。在正常操作期间,低功率HBM 110和高功率ASIC 105产生热,其中,高功率ASIC 105相对于每个低功率HBM 110产生更多的热量。

[0021] 低功率HBM 110和高功率ASIC 105经由插入器125耦合至封装基板115的表面。低功率HBM 110和高功率ASIC 105经由插入器125和封装基板115电连接至PCB 120。第一集成组件封装配置还包括耦合至封装基板115的封装盖130。该封装盖130覆盖多个低功率HBM 110和高功率ASIC 105。在正常操作期间,沉积在封装盖130与低功率HBM 110和高功率ASIC 105之间的第一热界面材料(TIM)145a减小了接触电阻,但是增加了在封装盖130与低功率HBM 110和高功率ASIC 105之间的热耦合。

[0022] 第一集成组件封装100还包括物理地热耦合至封装盖130的冷平板135。该冷平板

135包括基部表面和相对于封装盖130与基部表面相对的顶部表面。冷平板135还包括多个散热片。在正常操作期间,沉积在冷平板135的基部表面与封装盖130之间的第二热界面材料(TIM)145b减小了接触电阻,但是增加了在冷平板135与封装盖130之间的热耦合。

[0023] 第一集成组件封装100包括多个热电冷却(TEC)元件,诸如,在图1B的俯视图中示出的TEC 140a至140j(统称为TEC 140)。在图1A的侧视图中仅示出了第一TEC 140a和第二TEC 140b。参照图1B,TEC 140的大小被调整并且TEC 140被定位成沿与低功率HBM 110和高功率ASIC 105所耦合至的封装基板的表面垂直的方向突出的相应TEC 140的占用区的至少大部分与至少一个低功率HBM 110重叠。因此,如在图1B中示出的,沿与低功率HBM 110和高功率ASIC 105所耦合至的封装基板115的表面垂直的方向突出的TEC 140的占用区基本上没有部分基本上与高功率ASIC 150重叠。如在图1B中示出的,TEC元件的占用区都不与高功率ASIC 105重叠。

[0024] 在第一集成元件封装100中,TEC 140被集成到冷平板135中,使得每个TEC 140的第一侧被嵌入在冷平板135的基部表面中,并且每个TEC 140的第二侧物理地热耦合至封装盖130。在正常操作期间,第二热界面材料(诸如,位于冷平板135的基部表面与封装盖130之间的TIM 145b)减小了接触电阻,但是增加了在TEC 140、冷平板135和封装盖130之间的热耦合。通过将穿过冷平板135的基部表面的一个或者多个电连接150路由至PCB 120上的外部电源155来为TEC 140供电。通过使用闭环控制,调节了TEC的电压和电流以将低功率HBM 110的最大结温(Tj)维持在目标值。

[0025] 如上面提到的,在正常操作期间,低功率HBM 110和高功率ASIC 105产生热,其中,高功率ASIC 105相对于每个低功率HBM 110产生更多的热量。由于低功率HBM 110和高功率ASIC 105热耦合至封装盖130,因此,由低功率HBM 110产生的热在封装盖130中产生温度较低的局部区域,而由高功率ASIC 105产生的热在封装盖130中产生温度较高的局部区域。此外,TEC 140远离高功率ASIC 105,使得TEC 140更受由低功率HBM 140散发的热的影响,而不那么受由高功率ASIC 105产生的热的影响。TEC 140的这种放置帮助降低在封装盖130的覆盖低功率HBM 110的局部区域中的温度。进一步地,TEC 140放置在温度较低的局部区域中导致在TEC 140的热侧与冷侧之间的温度梯度较小,因此,相较于TEC更接近或者邻近高功率ASIC 105的情况,对TEC 140的COP的影响更小。此外,将低功率的HBM 110的冷却部分卸下到TEC 140允许冷平板135具有较高的热阻 (和较高的Tcase),同时使低功率HBM 110保持在热规范内。因此,使用TEC 140在对冷平板135的热性能的影响达到最小程度的情况下降低了低功率HBM 110在正常操作期间的温度。

[0026] 在一些实施方式中,冷平板可以包括多个绝缘槽口或者凹槽。图2是根据示例实施方式的第二集成组件封装200的侧视图的示意图。除了冷平板235之外,第二集成组件封装200与第一集成组件封装相似。冷平板235的基部表面包括多个绝缘槽口270。每个绝缘槽口270定位在邻近于集成到冷平板235的基部表面中的多个TEC 140中的一个TEC 140。在正常操作期间,绝缘槽口270将从高功率ASIC 105扩散的热最小化。

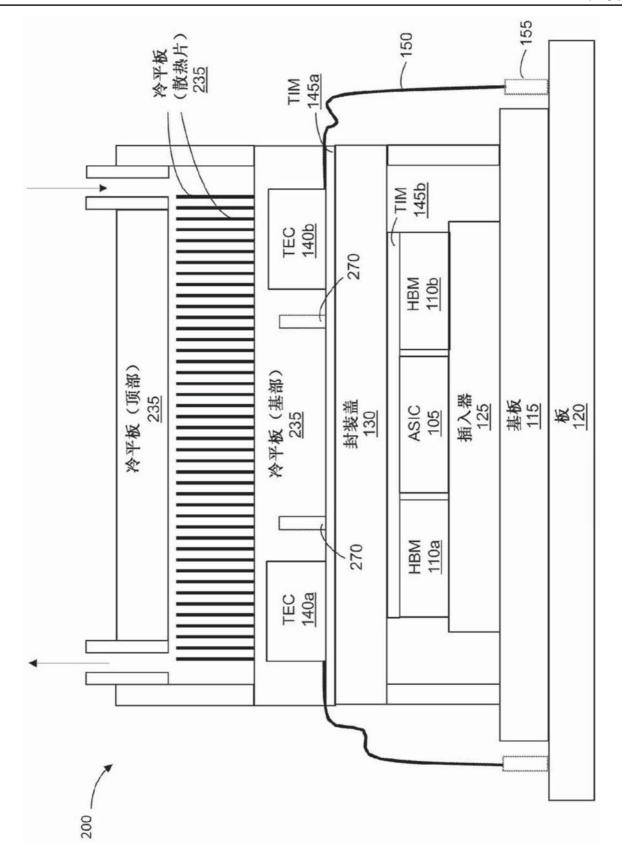

[0027] 在一些实施方式中,TEC元件可以被集成到封装盖而不是冷平板中。图3至图5图示了TEC元件被嵌入在封装盖内的封装配置。将TEC元件集成到封装盖而不是冷平板中使TEC元件更靠近低功率HBM组件放置,从而增加了由TEC在封装盖的覆盖低功率、对温度更敏感的HBM组件的局部区域处提供的特定位置冷却。使TEC元件更靠近HBM组件放置减少了由TEC

元件吸收的大功率ASIC产生的热量,但是增加了由TEC元件吸收的HBM产生的热量。在一些实施方式中,诸如,在图3和图4中示出的封装配置,可以将厚度小于大约1mm的超薄TEC元件嵌入到封装盖内的空腔中。在其它实施方式中,诸如,在图5中示出的封装配置,可以将厚度为大约2mm至大约4mm的标准现成TEC元件与封装盖集成。

[0028] 图3是根据示例实施方式的第三集成组件封装300的侧视图的示意图。第三集成组件封装300包括多个TEC 340和冷平板335。TEC 340被集成到封装盖330中,使得每个TEC 340的第一侧被嵌入在封装盖330a内,并且每个TEC 340的第二侧物理地耦合至冷平板335的基部表面。通过将穿过封装盖330a的一个或者多个电连接150路由至PCB 120上的外部电源155来为TEC 340供电。通过使用闭环控制,调节了TEC 340的电压和电流以将低功率HBM 110的最大结温(T,j)维持在目标值。

[0029] 图4是根据示例实施方式的第四集成组件封装400的侧视图的示意图。除了封装盖430之外,第四集成组件封装400与第三集成组件封装300相似。第四集成组件封装400包括多个TEC 440,该多个TEC 440被集成到封装盖430中,使得每个TEC 440的第一侧被嵌入在封装盖430内,并且每个TEC 440的第二侧物理地热耦合至低功率HBM 110。通过将穿过封装盖430的一个或者多个电连接150路由至PCB 120上的外部电源155来为TEC 440供电。通过使用闭环控制,调节了TEC 440的电压和电流以将低功率HBM 110的最大结温(Tj)维持在目标值。

[0030] 图5是根据示例实施方式的第五集成组件封装500的侧视图的示意图。除了封装盖530之外,第五集成组件封装500与第四集成组件封装400相似。TEC 540被集成到封装盖530中,使得每个TEC 540的第一侧耦合至冷平板135的基部表面,并且每个TEC 540的第二侧物理地耦合至低功率HBM 110。通过将穿过封装盖530的一个或者多个电连接150路由至PCB 120上的外部电源155来为TEC 540供电。通过使用闭环控制,调节了TEC 540的电压和电流以将低功率HBM 110的最大结温(Ti)维持在目标值。

[0031] 在一些实施方式中,独立地为TEC中的每个TEC供电。在一些实施方式中,可以调整TEC的大小并且将TEC定位为形成阵列。在阵列中的TEC的冗余将在正常操作期间的单独的TEC故障的负面影响最小化。在一些实施方式中,第一TIM 145a和第二TIM 145b可以包括导热脂、导热胶水、热填隙、导热垫或者导热粘合剂。

[0032] 图6是方法600的流程图,该方法600在被执行时可以产生在图1至图5中示出的封装。方法600包括:将多个低功率组件和高功率组件耦合至封装基板的表面,使得低功率组件位于邻近于高功率组件(阶段605)。多个低功率组件和高功率组件中的每一个在正常操作期间产生热,并且高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更多的热量。方法600进一步包括:将封装盖耦合至封装基板,使得封装盖覆盖多个低功率组件和高功率组件(阶段610)。方法600进一步包括:将冷平板物理地并且热耦合至封装盖,冷平板包括基部表面和顶部表面,其中,顶部表面相对于封装盖与基部表面相对(阶段615)。方法600还包括:在集成组件封装内调整多个热电冷却(TEC)元件的大小并且定位多个热电冷却(TEC)元件,使得沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的相应TEC元件的占用区的至少大部分与低功率组件中的至少一个低功率组件重叠,并且沿与低功率组件和高功率组件所耦合至的基板的表面垂直的方向突出的相应基本上没有部分基本上与高功率组件重叠(阶段620)。

方法600的示例实施方式在被执行时产生在图1至图5中示出的集成组件封装。如 [0033] 上面提到的,方法600包括:将多个低功率组件(例如,HBM 110)和高功率组件(例如,ASIC 105) 耦合至封装基板115的表面,其中,低功率HBM 110位于邻近于高功率ASIC 105,并且多 个低功率HBM 110和高功率ASIC 105中的每一个在正常操作期间产生热,并且高功率ASIC 105在正常操作期间相对于每个低功率HBM 110产生更多的热量(阶段605)。方法600进一步 包括:将封装盖130耦合至封装基板115,其中,封装盖130覆盖多个低功率组件HBM 110和高 功率ASIC 105(阶段610)。方法600进一步包括:将冷平板135物理地热耦合至封装盖130,冷 平板135包括基部表面和顶部表面,其中,顶部表面相对于封装盖130与基部表面相对(阶段 615)。方法600还包括:在集成组件封装内调整多个TEC 140的大小并且定位多个TEC 140, 使得沿与低功率HBM 110和高功率ASIC 105所耦合至的基板115的表面垂直的方向突出的 相应TEC 140的占用区的至少大部分与至少一个低功率HBM 110重叠,并且沿与低功率HBM 110和高功率ASIC 105所耦合至的基板115的表面垂直的方向突出的TEC 140的占用区基本 上没有部分基本上与高功率ASIC 105重叠(阶段620)。在一些实施方式中,方法600的阶段 620可以包括:将TEC 140集成到冷平板135中,使得将每个TEC 140的第一侧嵌入在冷平板 135的基部表面中,并且将每个TEC 140的第二侧物理地耦合至封装盖130。如在图2中的第 二集成组件封装配置200中示出的,在一些实施方式中,方法600的阶段620可以包括:将TEC 140集成到冷平板235的包括多个绝缘槽口270的基部表面中。每个绝缘槽口270定位在邻近 于被集成到冷平板235的基部表面中的多个TEC 140中的一个TEC 140。如在图3中的第三集 成组件封装配置300中示出的,在一些实施方式中,方法600的阶段620可以包括:将多个TEC 340集成到封装盖330中,使得将每个TEC 340的第一侧嵌入在封装盖330中,并且将每个TEC 340的第二侧物理地耦合至冷平板335的基部表面。在一些实施方式中,诸如,在图4中示出 的第四集成组件封装配置400,方法600的阶段620可以包括:将多个TEC 440集成到封装盖 430中,使得将每个TEC 440的第一侧嵌入在封装盖430中,并且将每个TEC 440的第二侧物 理地耦合至低功率HBM 110。在一些实施方式中,诸如,在图5中示出的第五集成组件封装配 置500,方法600的阶段620可以包括:将多个TEC 540集成到封装盖530中,使得将每个TEC 540的第一侧物理地耦合至冷平板135的基部表面,并且将每个TEC 540的第二侧物理地耦 合至低功率HBM 110。

[0034] 图7是在被执行时在正常操作期间控制在图1至图5中示出的集成组件封装中的温度的方法700的流程图。如上面提到的,在图1至图5中示出的集成组件封装包括覆盖位于邻近于高功率组件的多个低功率组件的封装盖,其中,高功率组件在正常操作期间相对于低功率组件中的每个低功率组件产生更高的热量。方法700包括:在较高热敏性的局部区域处提供对封装盖进行特定位置冷却,其中,较高热敏性的局部区域邻近于低功率组件,而较低热敏性的局部区域邻近于高温组件(阶段705)。方法700还包括:提供对封装盖的一些或者全部进行冷平板冷却(阶段710)。

[0035] 虽然在本文中讨论的低功率、对热更敏感的封装组件的主要示例是HBM组件,但是可以将具有相似热属性和限制(诸如,较低最大结温和高内部热阻)的其它组件包括在图1至图5中所示出的(并且在图6和图7中讨论的)集成封装配置内以便代替HBM组件或者除了HBM组件之外,通过TEC元件来进行主动式冷却。

[0036] 虽然本说明书包括了许多具体实施细节,但是不应该将这些细节视为对任何发明

或者可能要求保护的内容的范围的限制,而是作为对特定于特定发明的特定实施方式的特征的描述。在本说明书中在单独的实施方式的背景下描述的某些特征还可以组合地实施在单种实施方式中。相反,在单种实施方式的背景中描述的各种特征也可以单独地或者按照任何合适的子组合实施在多种实施方式中。此外,虽然上面可能将特征描述为以某些组合来起作用并且最初甚至同样地对该特征进行了要求,但是在一些情况下,可以从组合中删除来自所要求保护的组合的一个或者多个特征,并且所要求保护的组合可以指向子组合或者子组合的变化。

[0037] 同样,虽然在附图中按照特定顺序示出了操作,但是不应该将其理解为需要按照 所述的特定顺序或者按照相继的顺序来进行这种操作,或者需要进行所有图示的操作以实 现期望的结果。在某些情况下,多任务处理和并行处理可以是有利的。此外,不应该将在上 述实施方式中的各种系统组件的分离理解为在所有实施方式中需要这种分离,并且应该理 解,所描述的程序组件和系统通常可以一起集成在单个软件产品中或者封装到多个软件产 品中。

[0038] 可以将对"或者"的引用解释为包括的,使得通过使用"或者"描述的任何术语可以指示单个所描述的术语、一个以上所描述的术语和所有所描述的术语中的任何一种。标签"第一"、"第二"、"第三"等不一定旨在指示顺序,而是通常仅用于区别相同或者相似的项或者元件。

[0039] 对于本领域的技术人员而言,对本公开中所描述的实施方式的各种修改会是很显而易见的,并且在不脱离本公开的精神或者范围的情况下,本文中所定义的一般原理可以应用于其它实施方式。因此,权利要求书不旨在限于本文中所示出的实施方式,而是符合与本公开、本文中所公开的原理以及新颖特征一致的最广范围。

图1A

图1B

图2

图3

图4

图5

图6

图7